The Difference Between TTL LCD Screen and LVDS LCD Screen

Leave a message

The Difference Between TTL LCD Screen and LVDS LCD Screen

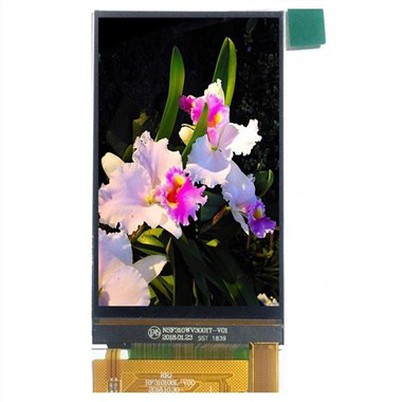

1. TTL screen interface description

The TTL signal is a standard signal that TFT-LCD can recognize, and the LVDS, TMDS and other signals used later are all derived from its code. Since the TTL signal level is about 3V, it has a great impact on high-speed and long-distance transmission, and the anti-interference ability is poor. The later LVDS interface effectively solved this problem. As long as the screen is above XGA, the interface method of LVDS is generally used.

Most of the early 12" and below screens are single 6-bit TTL interfaces. The connection pins on the screen are generally 41 pins and 31 pins, and the resolution is VGA (640X480) SVGA (800X600). Most of the 12" pins are 41, and the resolution is Yes: 800X600, the small screen below 10″ is mostly 31 pins, the resolution is 640X480, there are 22 6-bit TTL signal lines in total, (the least, electricity and ground are not counted), they are R, G, B three primary colors Signal, two HS, VS horizontal and vertical synchronization signals, one CK clock signal, one DE data enable signal. Among them, the three primary color signals of R, G and B have different numbers of data lines according to the number of digits of the screen, and there are 6 bits The signal line of the 6-bit screen is: R0~R5, G0~G5, B0~B5. The signal line of the 8-bit screen is: R0~R7, G0~G7, B0~B7. Three primary color signals It is a color signal, misplacement will cause the color confusion, and the other 4 (HS, VS, DE, CK) are control signals, and the wrong connection will cause the screen not to light up. It cannot be displayed normally.

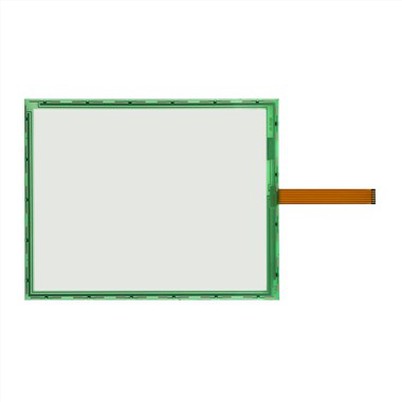

2. LVDS (low differential signal)

Its working principle is: the input TTL signal is encoded by a dedicated chip into an LVDS signal. A single 6-bit screen has 4 sets of differentials, (3 sets of data, 1 set of clock), and a single 8-bit screen has 5 sets of differentials (4 sets of data, 1 set of clock). The signal is defined as: D0-, D0+ | D1-, D1+ | D2-, D2+ | CK-, CK+ | D3-, D3+, if it is a single 6-bit screen, there is no D3-, D3+ group of data. The LVDS screen is also a TTL screen in the final analysis, because the signal level of LVDS is about 1V, and the interference between the - line and the + line can cancel each other, and the anti-interference ability is strong, which is very suitable for high-resolution screens.

Because the resolution of some high-resolution screens is too high, it is overwhelmed by one-way LVDS transmission alone, so dual-channel LVDS interfaces are used to reduce the rate of each channel of LVDS and improve signal stability. Dual 6-bit screens are 8 Group difference, (6 groups of data, 2 groups of clocks), double 8 screens are 10 groups of differences (8 groups of data, 2 groups of clocks).

Usually in the LVDS interface screen, mostly flat plugs. 14P, 20P, 30P, and there are also double-row 21P. 14P theoretically supports (single 6, single 8) bit screen, 20P, 21P theoretically supports (single 6, single 8, double 6) bit screen, 30P is possible

Compared with TTL screens, LVDS screens are much more single. It is much easier to measure and estimate. The interface of LVDS can be measured with a multimeter. First find the ground, then find the power supply. The power supply is together with the fuse, and then the signal. The signals of the LVDS screen are in pairs. The resistance is 100 ohms, generally (-, +, GND). The difficulty is to identify whether the clock is before or after the data.